Overview

To make the front-end SoC integration process reliable and correct by construction, a rich set of checking and verification features are provided as part of Defacto’s SoC Compiler platform.

Standalone and coherency checks between RTL and design collaterals (IP-XACT, UPF, SDC, LEF/DEF, etc.) are typical examples of the provided checks. Structural checks like connectivity, DFT and RTL code complexity are other examples of the provided DRCs. Customization and open APIs are typical characteristics of the SoC Compiler checks. SoC Compiler is certified ISO26262 and can be fully used in FuSa design flows.

High Level Benefits

- Monitor real time the IP integration process

- Validate quickly 3rd party source IPs

- One design centric checking solution instead of several tools to cover all coherency verification needs between RTL/ gate-level design and design collaterals: IP-XACT, UPF, Liberty, SDC, LEF/DEF

- Replace tedious simulation work with structural connectivity checks

- Detect and fix earlier testability issues

- Highlight complex and difficult to maintain RTL code

- Develop user-driven and custom checks

High Level Key Features

- Simulation-Free Connectivity Checks

- Design Centric Multi-View Coherency Checks including RTL, Gate-level, IP-XACT, SDC, UPF, LIBERTY and LEF/DEF

- UPF basic and advanced checks

- RTL DFT Signoff & Planning

- RTL advanced linting and code complexity metrics

Typical Applications

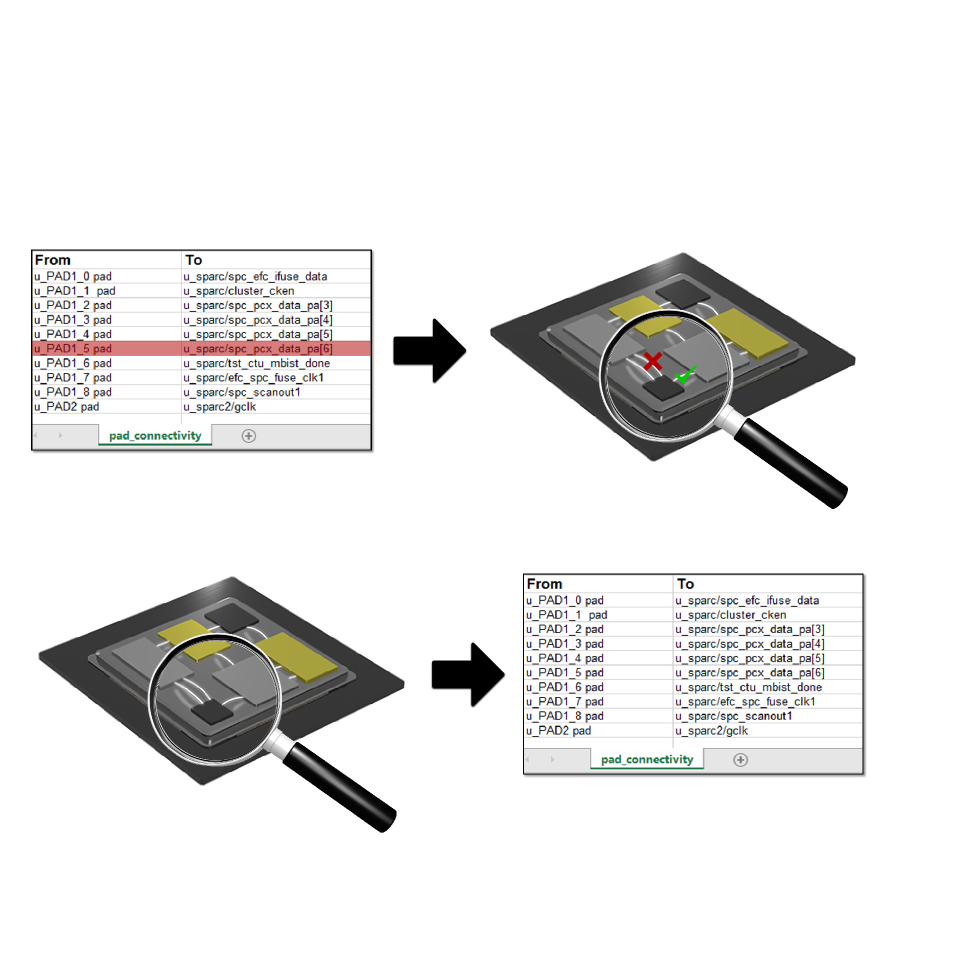

RTL Simulation-Free Connectivity Checks

Overview

Simulation-free RTL connectivity checking is the process that verifies that specifics pins, ports or nets are driven by the expected pins, ports or nets in a specific mode of operation. The modes are defined based on static constraints that are propagated throughout the design to enable specific paths.

Key Features

- Extract hierarchically all the design interconnectivity

- Report connectivity for different design objects

- Customizable reports

- Simulation free connectivity checks under constraints

- Constants propagation with GUI annotations

- Logic cone extraction

- Multiple filtering options

- Exhaustive check with no need to write verification testbench

- Easy creation of custom checks like for verification of memory pins connectivity, IO pad functional MUXing connectivity, Verification of clock gate enable logic, RTL connectivity checking for DFT MUXing logic, etc.

Design Centric Multi-View Checks including RTL, Gate-level, IPXACT, SDC, UPF, LIBERTY and LEF/DEF

Overview

During the SoC integration process, SoC Compiler manages the coherency between design description and all collaterals including: UPF, SDC, IP-XACT, LEF/DEF.

Key Features

- Design centric checks based on unified database

- RTL vs. libraries (Verilog, liberty, LEF)

- RTL vs. SDC

- RTL and liberty vs. UPF

- RTL vs. IPXACT

- RTL vs. netlist

- Quick inconsistencies pinpointing

- Coherency checks (DRCs)

- Syntax and parsing issues

- Unmatched objects/commands

- Quality checks (clocks, constraints on hierarchical pins)

- Customizable reporting

- Extensible set of checks

This email address is being protected from spambots. You need JavaScript enabled to view it.

RTL DFT Signoff - Testability DRCs & Test Coverage Evaluation

Overview

SoC Compiler allows designers and DFT experts to catch "test related" issues early in the design cycle, at RTL. It also allows the exploration of different DFT implementation options such as test points and estimates the impact on the design implementation steps. SoC Compiler helps making the right choices when it comes to DFT which saves time, effort as well as cost.

Key Features

- Complete DFT Design Rule Checks

- Enable running 3rd party ATPG at RTL

- Test coverage enhancement capabilities

- Clock / Reset controllability auto-fix

- Shadow logic insertion

- X generator analysis

- Test point insertion

- Accurate ATPG aware test coverage evaluation

- Automated flow for compression exploration

- Leverage UPF-based checks at RTL

- Automatic Test Point Exploration to estimate quickly the best Test Point tradeoff to reach several goals

- Target coverage

- Type and numbers of test points

- Location of inserted test points (hierarchy/clock domain/power domain)

- GUI interface

- Pinpoint root cause of DFT violations

- Test cartography for low coverage debug

- Hierarchical DFT exploration based on CTL models

- Ability to generate RTL with scan / Auto-fix logic

This email address is being protected from spambots. You need JavaScript enabled to view it.

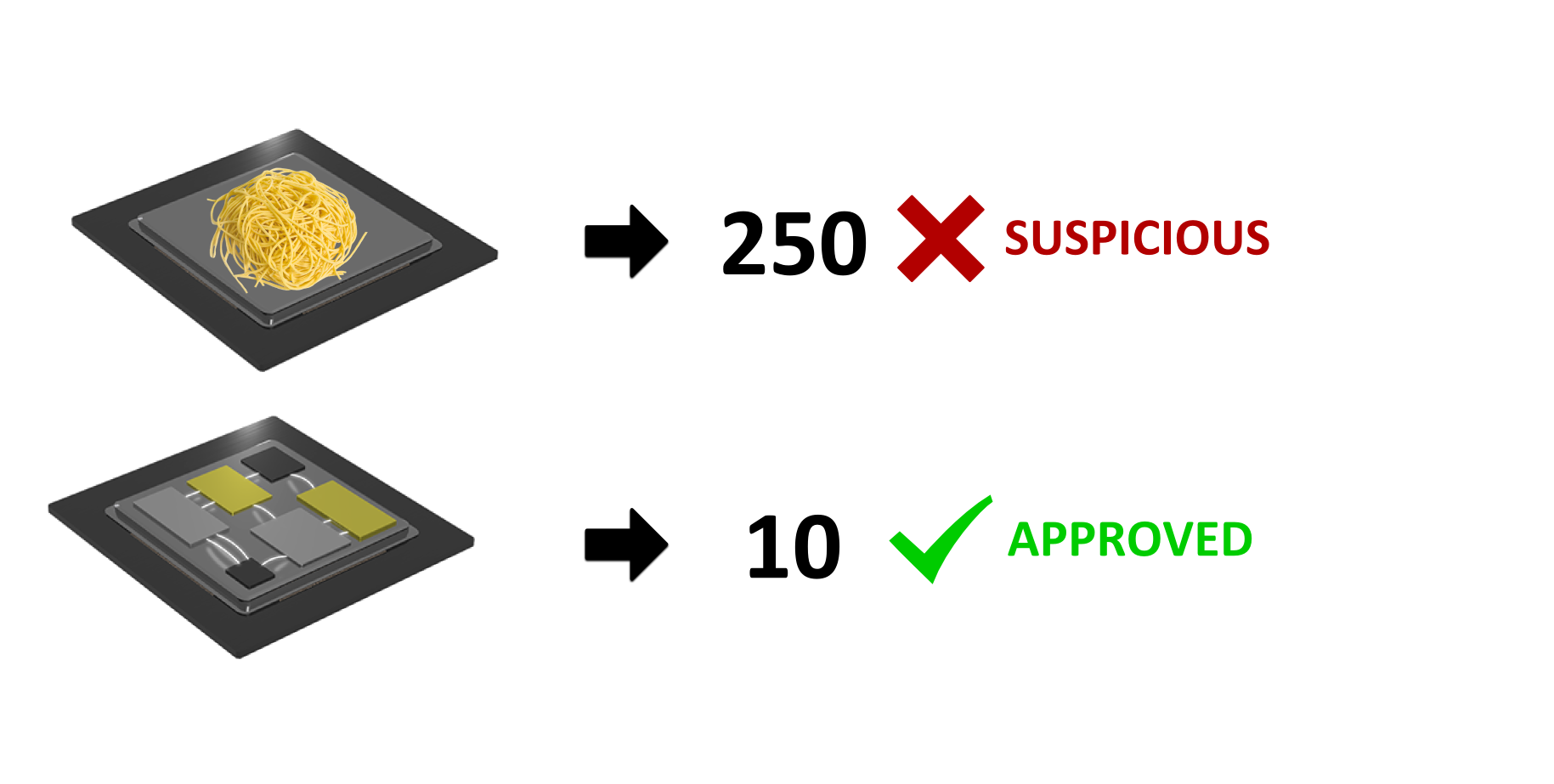

RTL Code Complexity Metrics

Overview

Through Code Complexity Metrics (CCM), SoC Compiler offers advanced RTL linting capabilities. CCM measures, captures the level of complexity of an RTL code (Verilog, VHDL, System Verilog) and let designers and design managers, better contain the increasing complexity of RTL databases. CCM also helps with preventing synthesis and post-synthesis problems by pinpointing critical areas of the RTL code

Key Features

- Automatically flag critical area of the RTL code which are difficult to maintain or to debug

- Code complexity score based on hardware and software metrics

- Data structure extraction (component, ports, instances, nets, connections)

- Monitor the complexity of a design during the SoC integration process

- Give the visibility of the balance between good program structure and code readability

- Custom reports in standard output formats (.xls, .html, .csv, etc.)

This email address is being protected from spambots. You need JavaScript enabled to view it.

Clock-tree Analysis and Visualization

Overview

This application enables a structural verification of complex clock paths with the capability to automatically detect the sequential elements of a design and tracing back from the clock pins to the drivers. This provides an automatic way of extracting the clock paths and generating various reports such as top level clocks and internal clocks, potential clocks, constraints to apply for potential clocks, tied clocks, etc.

SoC Compiler also provides the capabilities to graphically visualize complex clocks and reset trees through a highly configurable GUI to visualize.

Key Features

- Clock tree exploration

- Identification of clock sources (master/slave) and potential pin constraints

- SDC/XLS support for clocks / constraints definition

- Simulation free engine

- Pin constraints and RTL constants propagation

- Support for multiple working modes

- Dedicated DRC for master / generated clock path checks

- Reporting of path blockage

- Reporting of unexpected driver & clock shape mismatch

- Debug GUI environment

This email address is being protected from spambots. You need JavaScript enabled to view it.

For More Information :

Contact us or Access to Videos and Datasheets

Other products and solutions :

Front-End SoC Integration

Front-End SoC Integration Checks and Verifications

Checks and Verifications Open APIs and Customization

Open APIs and Customization