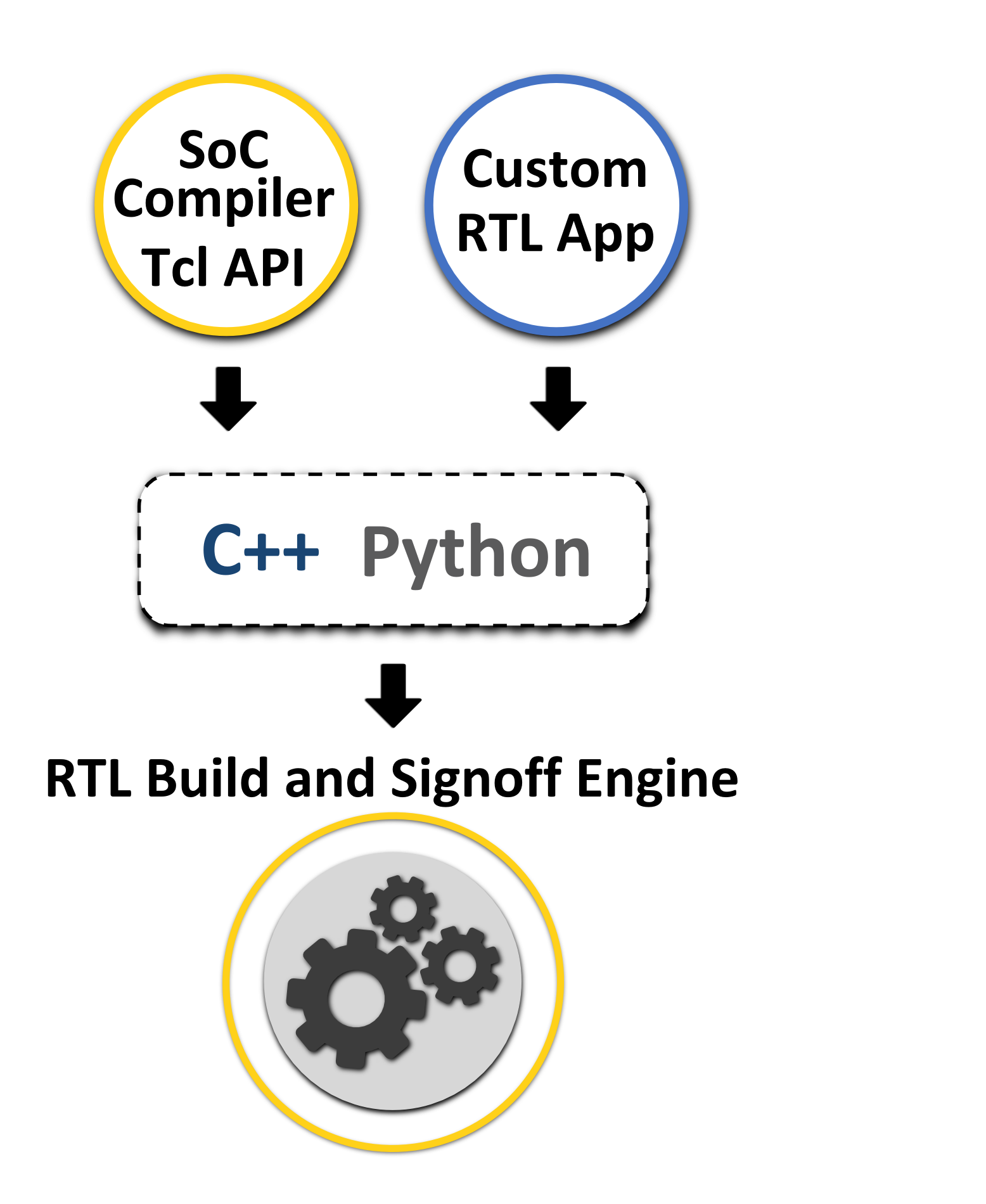

To make the pre-synthesis SoC integration process efficient and cost-effective, Defacto’s SoC Compiler provides a rich set of APIs which are accessible to a large number of users: RTL designers, architects, design verification engineers, power and clock management teams, DFT engineers and back-end engineers.

The provided APIs are either high or low-level according to the user needs with a high level of customization.

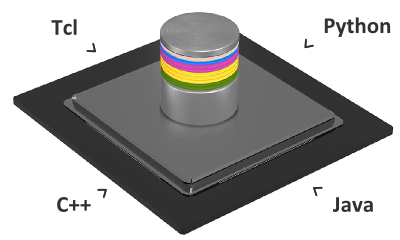

High-level APIs are dedicated to end-users with the support of several scripting languages: Python, Tcl, etc.

Low-level APIs are more dedicated to CAD teams who need to access the internal datastructure of SoC Compiler to better customize the flow for end users. The supported low-level languages are C++ and Python.

Benefits

- Accelerate software development by allowing developers to devote their time to meet software requirements

- Unify design data extraction through common APIs

- Easily migrate internal scripts and applications

- Improve the efficiency of creating new applications

- Help focusing on application requirements instead of the application infrastructure

- Portable solutions, from one design cycle to the next and across multiple projects

Features

- Provide unique customization capabilities

- User-friendly multi development language API

- C++, Python, Tcl

- Cost-effective custom EDA tool development

- File_list support for simplified RTL input management

- Common database and language independent API for any RTL format (Verilog, SystemVerilog, VHDL)

- Design hierarchy handling

- Advanced API for connectivity handling

- Easy plug-in development and integration with other tools

Typical Applications

- Connectivity extraction

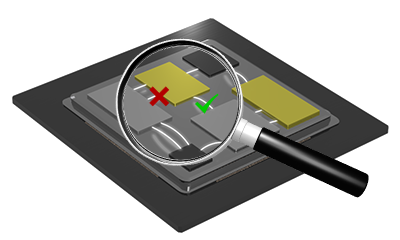

- Implementation of custom DRC engine for RTL quality verification & fixing

- SoC topology (hierarchy information) extraction

- RTL build and Integration

- Top level generation starting from sub-modules RTL definition

- IP integration using RTL and/or IP-XACT descriptions

- Design Manipulation

For More Information :

Other products and solutions :

Front-End SoC Integration

Front-End SoC Integration Checks and Verifications

Checks and Verifications Open APIs and Customization

Open APIs and Customization