SoCコンパイラ – 新世代のフロントエンドSoC設計

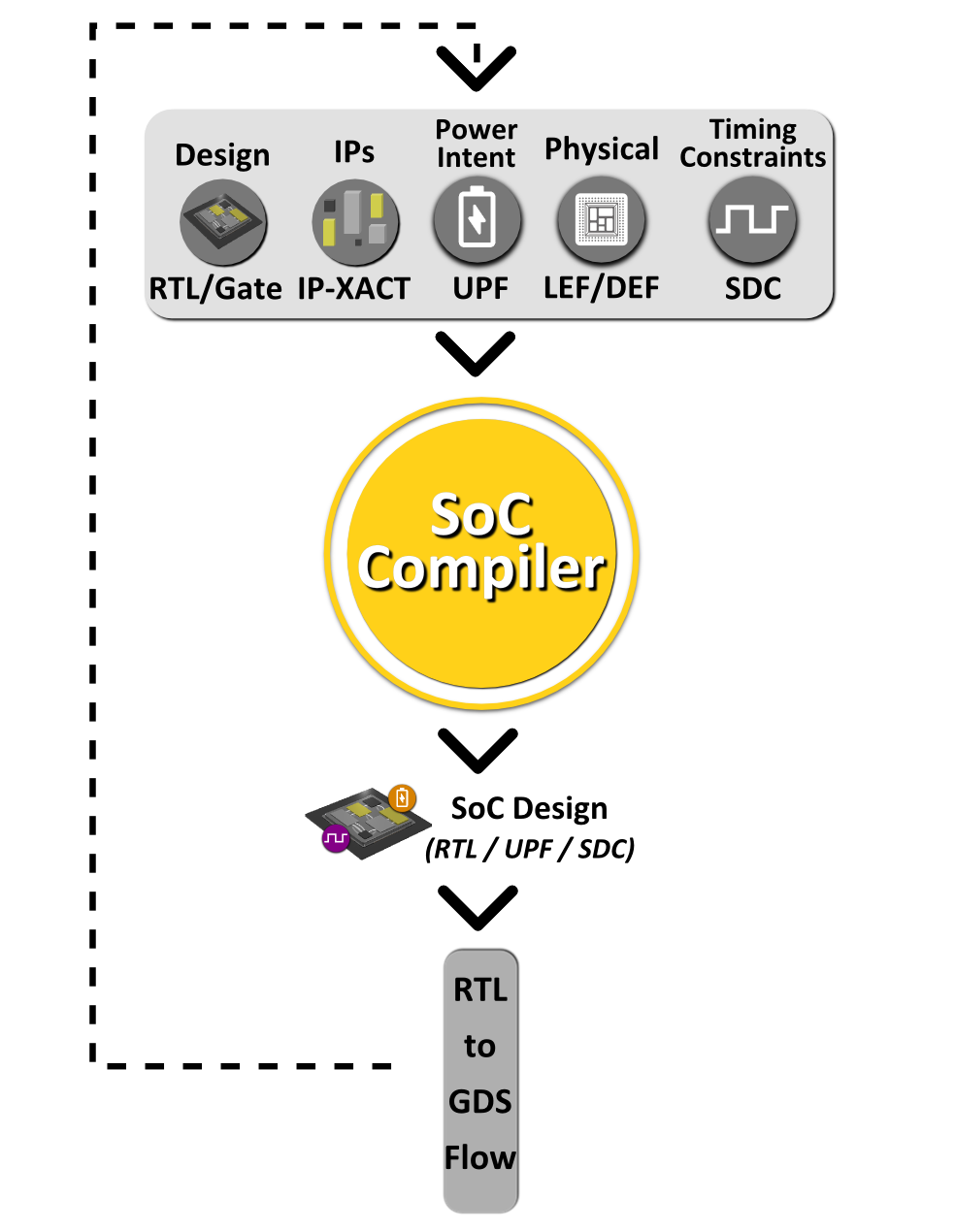

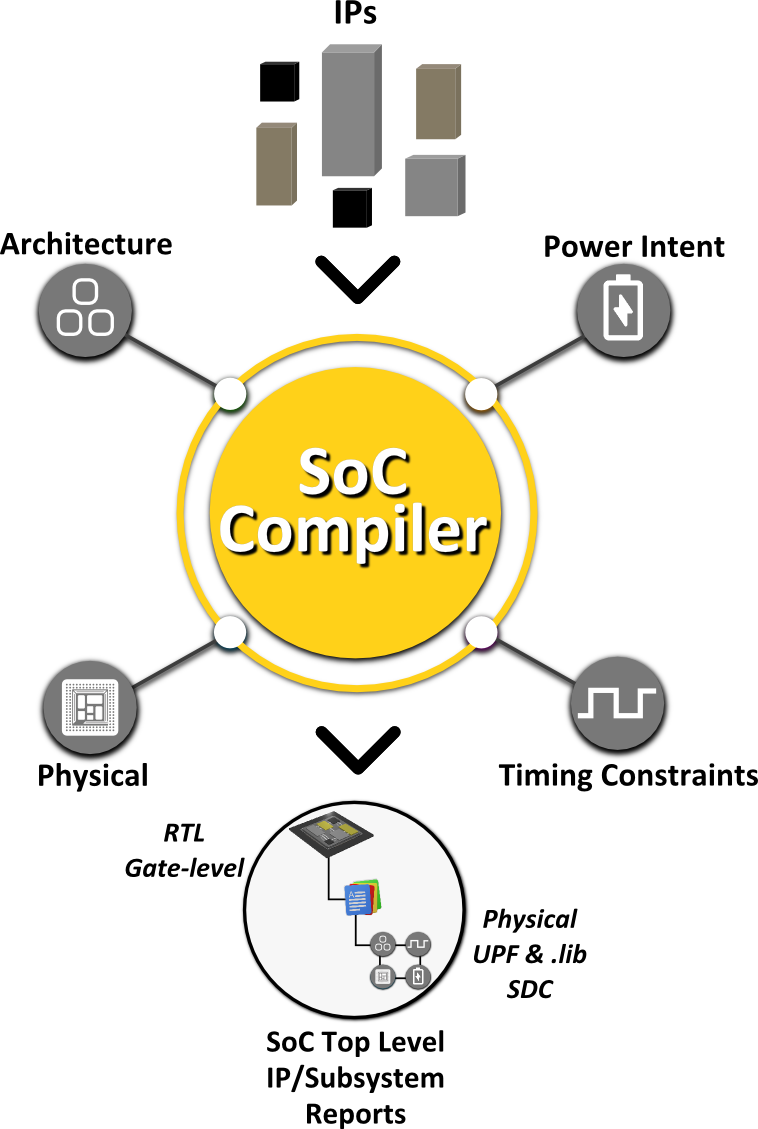

DefactoのSoC Compilerは、異なるAPIで統一されたデータベースを通じて、コスト効率の高いSoCビルド&サインオフ設計プロセスを可能にし、論理合成の前後で新しいSoC統合および設計最適化機能を提供します。

要約すると、SoC Compilerは論理合成前のSoCデザイン・アセンブリーにおいて、以下のようなRTLやデザインの付属データ管理に関する課題に対処するのに役立ちます。

- UPF : パワーフォーマット

- SDC : タイミング制約

- LEF/DEF : 物理設計フォーマット

- IPXACT : IP設計フォーマット

- Liberty : セルライブラリ

- など

また、SoC Compilerは、フィジカル制約、パワー制約、タイミング制約、DFT制約を考慮して、RTLからGDSフローRTL、UPF、SDCファイルを生成するための完全な自動化機能を提供しています。

フロントエンドSOCインテグレーション

DefactoのSoC Compilerは、RTL、IP-XACT、タイミング制約、パワー、フィジカル、テストなどのすべての設計情報を考慮し、高度に自動化された多次元的な合成前の完全なSoC統合プラットフォームです。

論理合成の前に、SoC CompilerはIPやコネクティビティの挿入、デザインの編集、統合の進捗状況をリアルタイムに確認できるビューの生成など、完全なインプリメンテーション機能を提供します。

これにより、数分でSoCを作成することができ、既存のプロジェクトからデザインを最大限に再利用することができます。

ハイレベルな利点

- 限られたスケジュールの中で、最適なPPAの組み合わせをサポートします。

- 論理合成前のSoC統合フローに自動化を提供します。

- RTL、IP-XACT、SDC、UPF、LEF/DEFなどのデザイン・コラタルを考慮することで、既存のSoCフロントエンドのアセンブリおよび統合フローを強化し、より統一された統合プロセスを実現します。

- RTLやデザインに付属するデータを含め、デザインの再利用率を最大90%以上に高めることができます。

- ハイレベルおよびローレベルの豊富なAPIをサポートすることで、内部スクリプトやツールを容易に移行することができます。Python、Tcl、Perl、C++、Javaなど。

- 設計の繰り返しを最小限にすることで、TATとエンジニアリング工数を大幅に削減できます。

- シンプルなAPIにより、専門家でなくても設計エンジニアリングタスク(パワー、アーキテクチャ、テストなど)を実行可能です。

- 設計ブロックやビューが欠けていても、SoCの作成が可能です。

ハイレベルな主要機能

- Verilog、System Verilog、VHDL、IP-XACT 2009、IP-XACT 2014などのマルチフォーマットIPコアの挿入が可能で、混在や未完成も可能です。

- System VerilogおよびIP-XACTインターフェースを含む、自動化された階層的な接続性の挿入

- SoC統合の進捗状況をリアルタイムに監視

- RTLでの物理的、電力的、タイミングを考慮した統合プロセス

- IPコアとサブシステムの設計再利用とパッケージング

典型的なアプリケーション

- RTLインテグレーション

- システムインテグレーション

- パワーインテグレーション

- クロックインテグレーション

- 物理的配慮のあるインテグレーション

詳細な情報は :

お問い合わせ または データシート、ビデオを見る

チェック&ベリフィケーション

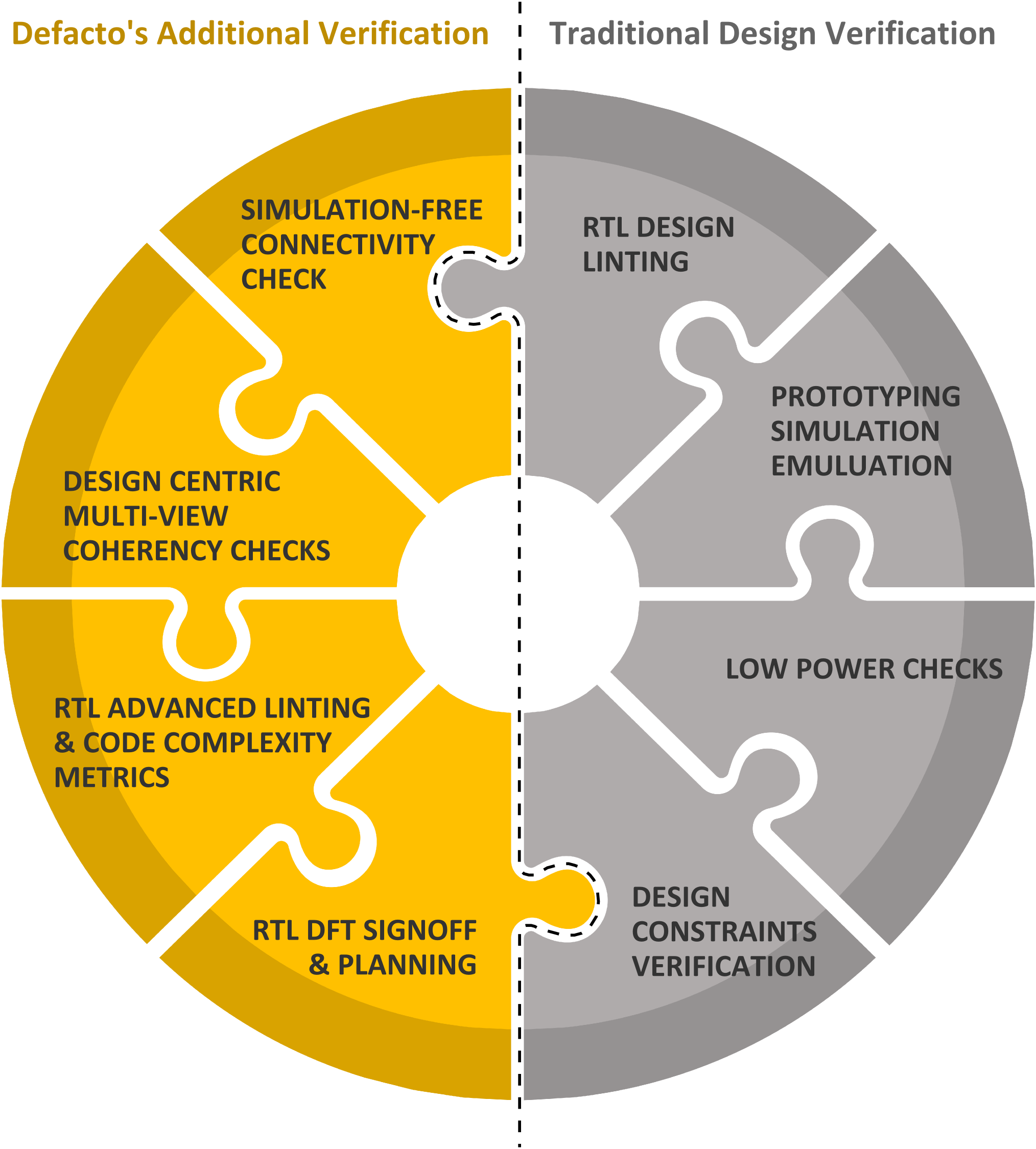

Defacto's SoC Compilerプラットフォームでは、フロントエンドのSoC統合プロセスを信頼性の高い正しい構造にするために、豊富なチェック機能と検証機能が提供されています。

RTLとデザイン・コラテラル(IP-XACT、UPF、SDC、LEF/DEFなど)の間のスタンドアロン・チェックとコヒーレンシー・チェックは、提供されているチェックの典型的な例です。また、接続性、DFT、RTLコードの複雑さなどの構造的なチェックも、提供されるDRCの一例です。カスタマイズとオープンAPIは、SoCコンパイラのチェックの典型的な特徴です。

ハイレベルな利点

- IP統合プロセスをリアルタイムに監視

- サードパーティのソースIPを迅速に検証

- RTL/ゲートレベル設計とデザイン・コラテラル間のコヒーレンシー検証のニーズを、複数のツールではなく、1つの設計中心の(IP-XACT, UPF, Liberty, SDC, LEF/DEF)チェック・ソリューションでカバーします。

- 面倒なシミュレーション作業を構造的な接続性チェックに置換

- テスト容易性の問題を早期に発見し、修正

- 複雑で保守が困難なRTLコードのハイライト

- ユーザー・ドリブンなカスタム・チェックの開発

ハイレベルな主な機能

- シミュレーション不要の接続性チェック

- RTL、ゲートレベル、IP-XACT、SDC、UPF、LIBERTY、LEF/DEFを含むデザインセントリックなマルチビューコヒーレンシーチェック

- UPFベーシックチェックとアドバンスチェック

- RTL DFTサインオフおよびプランニング

- RTLアドバンスドリンティングとコード複雑性メトリクス

典型的なアプリケーション

- RTLシミュレーション不要の接続性チェック

- RTL、ゲートレベル、IPXACT、SDC、UPF、LIBERTY、LEF/DEFを含むデザインセントリックなマルチビュー・チェック

- RTL DFTサインオフ - テスト容易性DRCs & テストカバレッジ評価

- クロックツリー解析と可視化

詳細な情報は :

お問い合わせ または データシート、ビデオを見る

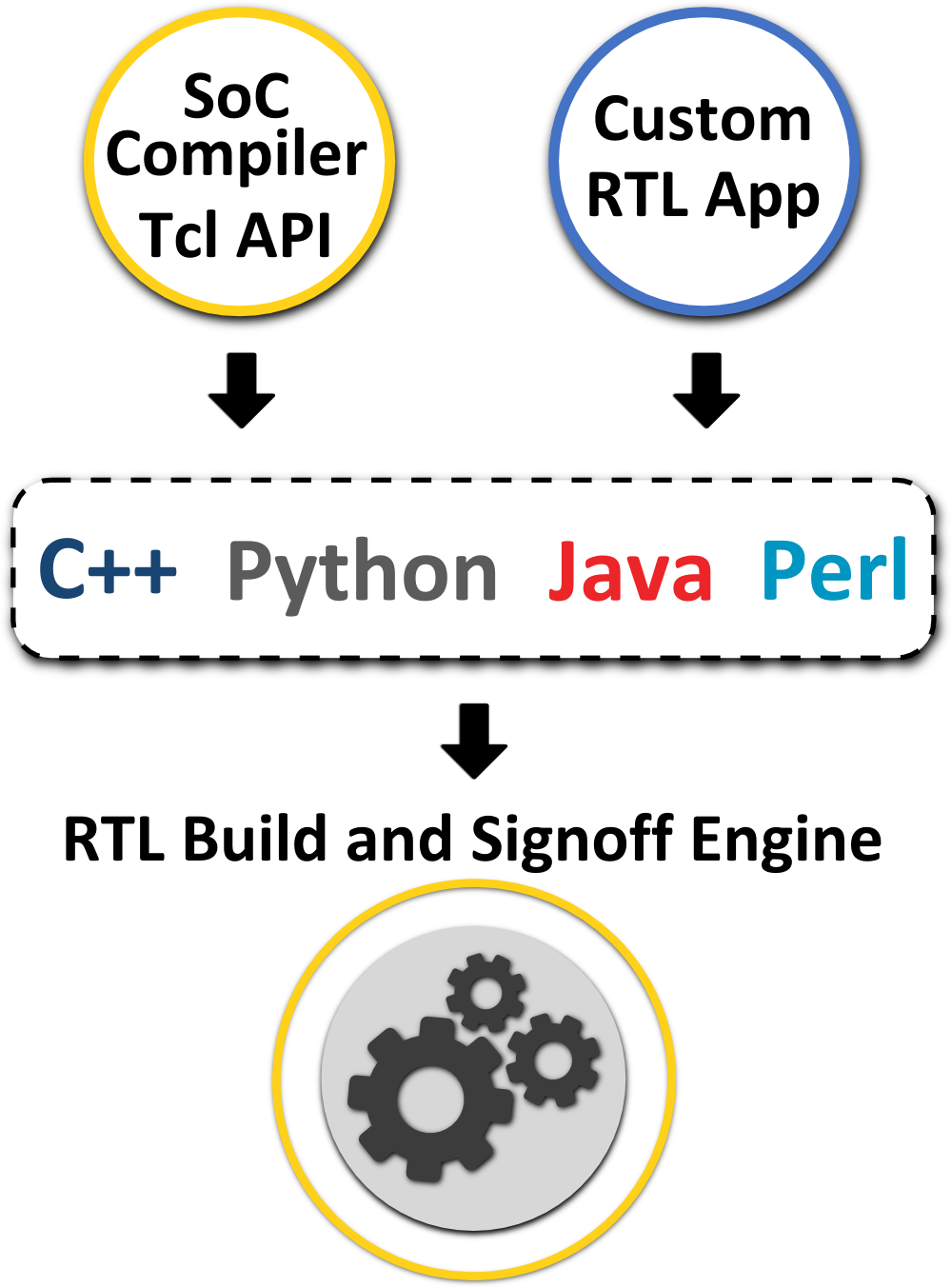

オープンAPIとカスタマイズ

合成前のSoCインテグレーション・プロセスを効率的かつコスト効率の高いものにするために、DefactoのSoC Compilerは、多くのユーザーが利用できる豊富なAPIを提供しています。RTL設計者、アーキテクト、設計検証エンジニア、電源・クロック管理チーム、DFTエンジニア、バックエンド・エンジニアなど、多くのユーザーが利用できます。

提供されるAPIは、ユーザーのニーズに応じてハイレベルまたはローレベルのいずれかであり、高度なカスタマイズが可能です。

ハイレベルのAPIは、複数のスクリプト(Python、Tcl、Perlなど)言語をサポートし、エンドユーザーに特化しています。

一方、ローレベルのAPIは、エンドユーザー向けにフローをカスタマイズするためにSoC Compilerの内部データ構造にアクセスする必要があるCADチームに適しています。サポートされているローレベル言語には、C++とJavaがあります。

ハイレベルな利点

- 開発者がソフトウェアの要件を満たすために時間を割くことができるため、ソフトウェア開発が加速可能

- 共通のAPIを使用して設計データを抽出することが可能

- 内部スクリプトやアプリケーションの移行が容易

- 新規アプリケーション作成の効率化

- アプリケーションのインフラストラクチャではなく、アプリケーションの要件に集中することができる

- 設計サイクルから次の設計サイクルまで、また複数のプロジェクトにまたがって使用できるポータブルなソリューションを提供

ハイレベルな主な機能

- 独自のカスタマイズ機能を提供

- ユーザーフレンドリーなマルチ開発言語API

- C++、Java、Perl、Tcl、Ruby、Python

- 費用対効果の高いカスタムEDAツールの開発

- RTLの入力管理を容易にするFile_listのサポート

- あらゆるRTLフォーマット(Verilog、Sverilog、VHDL)に対応する共通のデータベースと言語に依存しないAPI

- デザイン階層の処理

- 接続性処理のための高度なAPI

- プラグイン開発や他のツールとの統合が容易

典型的なアプリケーション

- 接続性の抽出

- RTL品質検証および修正のためのカスタムDRCエンジンの実装

- SoCトポロジー(階層情報)の抽出

- RTL構築と統合

- サブモジュールのRTL定義からのトップレベル生成

- RTLおよび/またはIP-XACT記述を使用したIP統合

- デザインの操作性

詳細な情報は :

お問い合わせ または データシート、ビデオを見る

SoCコンパイラ – 新世代のフロントエンドSoC設計

デファクト社、フロントエンドのSoC統合プラットフォームをアップグレード

2021年4月26日 アンネ・フランソワーズ・ペレ

Defacto Upgrades Front-end SoC Integration Platform - EE Times Europe

アプリケーションの高度化に伴い、システム・オン・チップ(SoC)の設計はますます複雑化しています。RTL(レジスタ・トランスファー・レベル)レベルの設計ソリューションを提供するフランスのDefacto Technologies社は、統一されたSoC統合プラットフォームを発表しました。このプラットフォームは、フロントエンドのタスクを自動化し、設計フローの早い段階で意思決定を行うことができるため、設計プロセスの時間短縮とコスト削減につながります。

"Defacto Technologies社のCEOであるChouki Aktouf氏は、EE Times Europeの取材に対し、「今日、私たちは、設計データ(RTLまたはゲートレベル)、パワーインテント、電子システム設計(IP-XACT)、レジスタ仕様、タイミング制約、ハードウェアとソフトウェア間のインターフェースなど、複数の次元を考慮しながら、最大限の自動化でSoCを迅速に構築する必要がある。」と述べています。

SoCの統合段階で、これらの要素をすべて把握するにはどうすればよいのでしょうか。Defacto社は、SoCを物理的に構築する前に、異なる情報(RTL、ゲートレベル、UPF、LIBなど)を読み取って考慮できるように構造化された共通のデータベースを開発したと述べています。"SoC Compilerは、論理合成やコンパイルの準備を支援することを目的としていますとAktouf氏は述べています。

最新SoC Compilerは、デファクトのStar SoC統合ソリューションv9メジャーリリースされました。

自動化

SoCの設計は、複雑なプロセスとなっており、連続した、しかし依存性のあるステップでの区分けが必要となっています。そのため、設計プロセスの統一と自動化の重要性が高まっています。

Defacto claims SoC Compilerは、設計フローの初期段階で物理的制約を考慮するフロントエンドを自動化します。例えば、Aktouf氏は次のように述べています。「同じパワー・ドメインに属するすべてのブロックを抽出したい場合、RTL、それに付随するすべてのライブラリ、UPFを通じて表現されたパワー・インテント・アーキテクチャに関連するすべての情報を抽出しなければなりません。このソリューションは、正しいファイルを取得し、ファイル間の整合性を管理して、この順序を実行できるものでなければなりません。」

SoC設計プロジェクトでは、ほとんどの場合、カスタマイズが必要です。"Aktouf氏は次のように述べています。「カスタム検証を追加して実行する必要がある場合、ソリューションはそれを可能にしなければなりません。"また、変更を加えるとすぐに自動的に反映され、フロー全体で見えるようにしなければなりません」。

現在、SoCの設計プロジェクトには、分散した複数のチームが参加しています。更新や不整合の検出は、リアルタイムで、すべてのチームに見えるようにしなければなりません。

"一貫性に問題がある場合、UPFファイルが存在しないためにこのブロックをある階層から別の階層に移動させることができない場合、ツールはフラグを立てるべきです」とAktouf氏は述べています。

SoC Compilerは、各タスクが他のタスクに与える影響を自動的に評価し、エラーを特定します。

デファクト社によると、SoC Compilerはほとんどのスクリプト言語(Python、Perl、Tclなど)で使用でき、コマンドをより複雑なRTLコード(VHDL、Verilog、System Verilog)に自動的に変換するという。例えば、「インドでIPを担当しているエンジニアは、Tcl言語のエキスパートです」とAktouf氏は説明しています。シリコンバレーのエンジニアは、別のブロックを担当していて、Python言語のエキスパートです。彼らが思い通りに表現できるプラットフォームでなければなりません」。APIは、異種混合で複数の拠点を持つチームにとって不可欠なものです。

SoC Compilerは、5つの統合ツールを中心に構築されており、統一された自動設計フローを実現します。RTLデザイナー、RTL IPインテグレーション、RTLローパワー、RTL DFT、そしてRTLデザインチェッカーです。

設計の再利用

市場投入までの時間は非常に重要です。設計サイクルを短縮するための一般的なアプローチは、以前の設計のサブセットを新しい設計で再利用することです。SoC Compilerでは、あるプロジェクトのために書かれたコードを別のプロジェクトで再利用することができます。"古いプロジェクトがあれば、この古いプロジェクトのIPやサブシステムを自動的にパッケージ化して共有し、新しいプロジェクトに使用することができます。

" さらに、「このソリューションにより、合成やコンパイルのフェーズの前にSoCを構築することが可能になるだけでなく、IPやサブシステムをパッケージ化することで、再利用率を最大化し、コストを削減することができます」と述べています。"

設計の繰り返し

SoCの設計サイクルは限られた時間の中で行われ、テープアウトしたものを生産に移さなければならないため、それを超えることはできません。さらに重要なことは、企業は投資収益率を最大化するために、市場に最初に投入しなければならないということです。そのためには、エンジニアリングコストを抑えながら、厳しい納期の中で、最も困難な設計のPPA(パワー、パフォーマンス、エリア)を最大化することが課題となります。"Aktouf氏、「統一された多次元的なソリューションを持つことで、フローの中での繰り返しを避けることができます。"私はシステムレベルから始めて、下に向かって作業し、物理的なレベルに到達し、2回目の反復で戻ってきて、洗練され、最適化します。通常、繰り返しの回数は多いのですが、私たちはその回数を減らすお手伝いをします」。

物理レベルの専門家がレイアウトを見て、『この2つのIPブロックは隣り合う必要がありますが、このIPブロックは離れている必要がある』場合、配線や配置の問題を考慮してアーキテクチャレベルで何をすべきかを理解するための分析が行われるとAktouf氏は説明します。

"物理を考慮したSoCの構築やアセンブリと呼ばれるものは、労力を削減し、高いPPA効率を達成し、結果としてパフォーマンスを向上させるために非常に重要」とAktouf氏は述べています。

Defacto社によると、SoC Compilerはすべての主要ベンダーの既存のEDAツールフローに統合されます。また、OpenFive社やSipearl社などの企業でもテストされています。

詳細な情報は :

お問い合わせ または データシート、ビデオを見る