Daniel Nenni (Semiwiki): When I was at DAC last month, I had the chance to talk with Chouki Aktouf and Bastien Gratréaux from Defacto and they told me about a new innovative solution to generate Arm-based System-on-Chips. I heard that this solution has now been released.

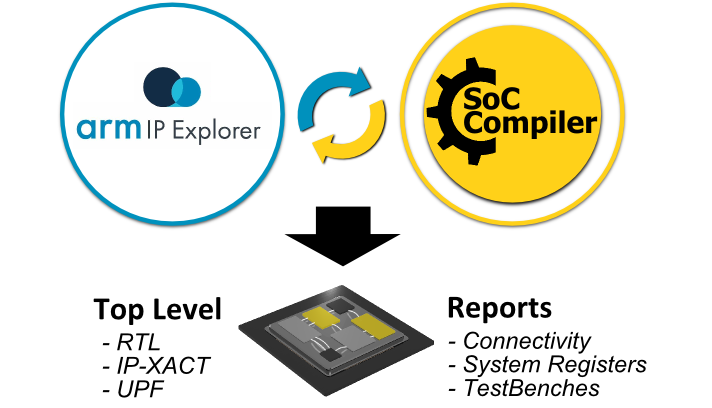

Defacto and Arm developed a joint SoC design flow to help Arm users cover all needed automation—from SoC design architecture and exploration to top-level generation of all needed files for implementation and verification flows.

Through the intuitive graphical interface from the Arm design platform, Arm IP Explorer, helps make specification of the SoC easy and user friendly. Once SoC exploration is realized, RTL and IP-XACT design files are automatically generated using Defacto’s SoC Compiler design solution.

The jointly developed solution is built around a strong link between Arm IP Explorer and Defacto’s SoC Compiler to enable users to generate quickly several SoC design configurations. The speed of the Defacto SoC Compiler enables the generation of a multitude of SoC configurations based on different user specifications. With this solution, the overall design time from specification to an SoC ready for synthesis can be significantly reduced.

Why was this solution needed?

With the complexity of current SoC designs and the design space possibilities, designers and architects face significant challenges when exploring SoC architectures. They traditionally access an IP database, where they select, configure, and download IP. The following step is to connect the IPs to build the complete SoC design database which is ready for logic synthesis. Iterative work is usually needed for each of the configurations created, which impacts overall turn-around time (TAT).

Providing a comprehensive and automated design solution from specification to implementation with all necessary exploration metrics, such as chip size, power consumption, and so on, is needed more than ever.

How it works?

The joint Arm IP Explorer/SoC Compiler solution is the shortest path from the definition of Arm-based system architecture to implementation and design verification.

The first step is that users access Arm IP Explorer and start selecting IP cores from the catalog. IP parameters can be set at this level and IP configuration in general is made easy. With the selected IPs, users can architect the complete system. The platform gives also the flexibility to add custom IPs to reflect the desired system. At this stage, an estimation of the overall size of the SoC is provided.

Integration checks are performed on-the-fly to ensure that the built SoC is correct including all needed and complex connectivity. The completed and validated system is then exported into the Defacto SoC Compiler, which automatically generates the top-level IP-XACT / RTL / UPF files, along with different reports. These reports provide detailed connectivity density, chip size, and power consumption.

The generated files are fully compatible with standard RTL2GDS SoC design flows and can be provided directly to both logic synthesis tools and design verifications tools. With the simplicity, speed, and flexibility of this solution, users can quickly and automatically explore and generate several SoC design configurations.

Who is this solution for?

This solution has been developed for Arm users who need to quickly build new Arm-based SoC configurations. Using this solution users increase efficiency and productivity, making easy to find and compare Arm IPs in a unique source. With the simplified IP configuration, coupled with the automatic generation of the top level SoC, users are drastically reducing costs and time to market.

This flow has already been validated for a large number of systems and is ready to be used for several applications such as IoT, automotive, mobile, 5G, cloud computing, HPC, AI, etc.