What Does it Do?

In EDA there are lots of special interest groups that tend to create their own narrowly defined sub-flows and file formats, eventually gaining enough momentum to form a standard, so that multiple vendors can compete and cooperate in a bigger design flow. Here are some of the standards in use today for SoC design:

- Design Data, RTL or Gate-level

- IP block descriptions, IP-XACT

- Power Intent, UPF

- Physical cells, LEF/DEF

- Timing constraints, SDC

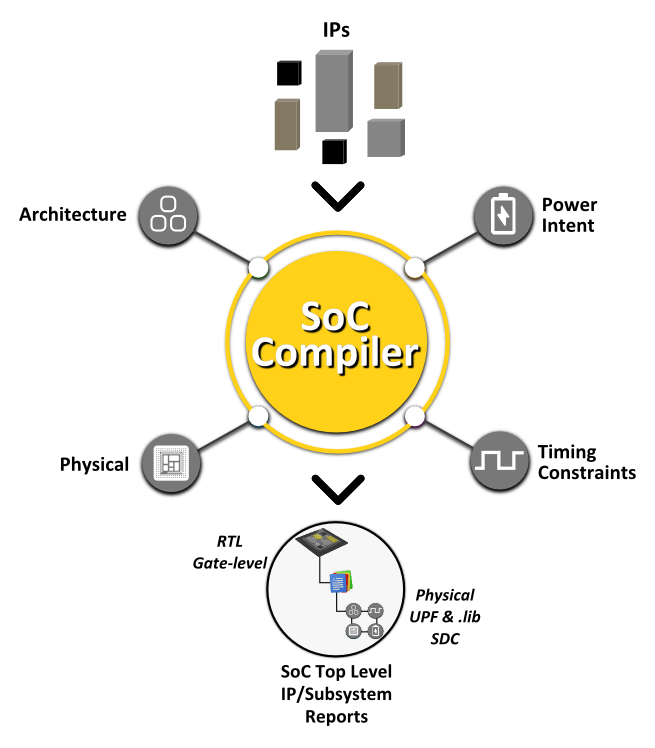

In the SoC Compiler tool it accepts as input all of these formats, then enables an engineer to efficiently and quickly assemble and create a new SoC, getting the RTL and design collateral ready for logic synthesis. Here’s the Defacto tool flow:

Modern SoCs can have hundreds of IP blocks, and when those blocks use the IP-XACT standard they can be read into SoC Compiler to check for correctness and a hierarchy can be quickly built for a new design. Defacto is a member of Accellera, and their tool works with the IP-XACT 2009 and 2014 standards. You can even write scripts to control how your IP blocks should be connected together, saving time from making manual file edits.

RTL design editing is made easier by the use of scripts or API languages like Tcl and Python, and SoC Compiler understands that when the RTL design is changed that the SDC and UPF collateral files also need to be updated automatically. Error-prone manual editing of SDC and UPF files in coherency with RTL changes is a thing of the past when using SoC Compiler.

Based on physical information contained in LEF/DEF files, SoC Compiler assists in the SoC creation, by being physically aware in order to optimize connectivity insertion. This helps in reducing the width of routing channels which helps in reducing the chip area.

SoC Compiler also provides the capabilities to explore and understand the Power intent and clock trees. A large set of linting checks are part of the embedded parser to ensure correctness, proper syntax and semantics for UPF and SDC files in conjunction with RTL.